## FIFO Systems with Interleaved Regulators

Jean-Yves Le Boudec<sup>1</sup>

WoNeCa 2018

Erlangen, 28 February 2018

<sup>1</sup> https://people.epfl.ch/105633/research

#### Contents

- 1. FIFO Networks and Interleaved Regulator

- 2. Pi-Regulation

- 3. Delay Bound for Interleaved Regulator

Abstract: We define the minimal interleaved regulator, which generalizes the Urgency Based Shaper that was recently proposed by Specht and Samii as a simpler alternative to per-flow reshaping in deterministic networks with aggregate scheduling. With this regulator, packets of multiple flows are processed in one FIFO queue; the packet at the head of the queue is examined against the regulation constraints of its flow; it is released at the earliest time at which this is possible without violating the constraints. Packets that are not at the head of the queue are not examined until they reach the head of the queue. This regulator thus possibly delays the packet at the head of the queue but also all following packets, which typically belong to other flows. However, we show that, when it is placed after an arbitrary FIFO system, the worst case delay of the combination is not increased. This shaping-for-free property is well-known with per-flow shapers; surprisingly, it continues to hold here. To derive this property, we introduce a new definition of traffic regulator, the minimal Pi-regulator, which extends both the greedy shaper of network calculus and Chang's max-plus regulator and also includes new types of regulators such as packet rate limiters. Incidentally, we provide a new insight on the equivalence between minplus and max-plus formulations of regulators and shapers.

[Le Boudec 2018] Le Boudec, Jean-Yves, "A Theory of Traffic Regulators for Deterministic Networks with Application to Interleaved Regulators", arXiv preprint arXiv:1801.08477.

#### 1. FIFO Per-Class Networks

FIFO per class are commonly used in Time Sensitive Networking (IEEE 802.1 TSN, IETF Detnet).

Computing backlog and delay bounds is hard [Boyer et al 2012] [Bouillard-Stea 2015][Bondorf et al 2017].

Example: [Le Boudec-Thiran 2001, Section 6.4]

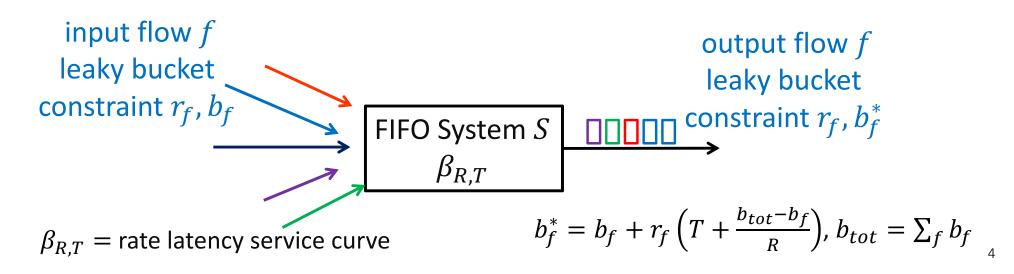

#### **Burstiness Cascade**

Burstiness of every flow increases at every hop as a function of other flows' burstiness:

$$b_f^* = b_f + r_f \left(T + \frac{b_{tot} - b_f}{R}\right), \quad b_{tot} = \sum_i b_i$$

Increased burstiness causes increased burstiness (cascade).

Good delay bounds depend on the topology and on the number of hops. In non-feedforward nets, delay bounds are generally bad except at low utilizations and small numbers of hop [Bennett et al 2002].

## **Avoiding Burstiness Cascade**

Solution 1: re-shape every flow at every hop (per-flow shaping) Solves the problem but defeats the purpose of per-class network.

#### Solution 2: Interleaved Regulator

- FIFO queue of all packets of all flows in class

- packet at head of queue is examined versus traffic regulation of its flow; this packet is delayed if it came too early

- packets not at head of queue wait for their turn to come

[Specht-Samii 2016] "Urgency Based Scheduler", now called "Asynchronous Traffic Shaping" at IEEE TSN

[Specht and Samii 2016] compute delay bounds for FIFO networks with interleaved regulators, using trajectory analysis.

Question 1: what can we say of worst-case delay due to Interleaved Regulator?

[Specht-Samii 2016] considers two types of traffic rules

- 1. Leaky Bucket rule : Arrival curve  $\sigma(t) = rt + b$  (min-plus calculus)

- 2. LRQ-rule:  $A_n \ge A_{n-1} + \frac{L_{n-1}}{r}$  ( $A_n$ : arrival time of packet n,  $L_n$ : length of packet n) LRQ-rule is a g-regulator as defined by C-S Chang (max-plus calculus) [Chang-Lin 1998]

LRQ is not an arrival curve; arrival curve is not a g-regulator.

Question 2: can we make a theory of interleaved shaper that applies both to arrival curve and g-regulator?

## 2. Pi-Regulation

A single packet flow (A, L)  $A = (A_1, A_2, ...)$  packet arrival times,  $A \in \mathcal{F}_{inc}$   $L = (L_1, L_2, ...)$  packet lengths  $\Pi$  a mapping  $(A, L) \to \Pi(A, L) = (E_1, E_2, ...) \in \mathcal{F}$  (eligibility times) This flow is  $\Pi$ -regular  $\Leftrightarrow A \geq \Pi(A, L)$  i.e.  $A_n \geq E_n$

We require that  $\Pi$  is causal ( $E_n$  depends only on  $A_1$ , ...,  $A_{n-1}$  and  $L_1$ , ...,  $L_n$ ), homogeneous (invariant by change of time origin) and isotone (if  $A \ge A'$  then  $\Pi(A, L) \ge \Pi(A', L)$ ).

## Chang's g-regularity

Flow (A, L) is g-regular  $\Leftrightarrow A_n - A_m \ge g(L_m + \dots + L_{n-1})$  [Chang-Lin 1998] [Chang 2002]

This is  $\Pi$ -regulation with

$$\Pi(A, L)_n = \max_{1 \le m \le n-1} \{A_m + g(L_m + \dots + L_{n-1})\}$$

LRQ-rule is a special case:

$$\Pi^{LRQ(r)}(A, L)_{n} = A_{n-1} + \frac{L_{n-1}}{r}$$

$$\Pi^{LRQ(r)}(A, L)_{1} = -\infty$$

#### Max-Plus and Arrival Curve Constraints

We need a max-plus formulation of arrival curve constraints.

Min-plus / max-plus duality is solved by Liebeherr [Liebeherr 2017] who shows the following equivalence:

| Min-plus                                       | Max-plus                                                       |

|------------------------------------------------|----------------------------------------------------------------|

| Cumulative arrival function                    | Arrival time function                                          |

| $R(t) = \sum_{n} A_n 1_{A_n < t}$              | $T(x) = \inf_{n} \left( A_n 1_{L_1 + \dots + L_n > x} \right)$ |

| Arrival curve $\sigma(t)$                      | Max-plus traffic enveloppe $\lambda(x)$                        |

| $R(t) - R(s) \le \sigma(t)$                    | $T(y) - T(x) \ge \lambda(y - x)$                               |

| $T=R^{\uparrow}$ , $\lambda=\sigma^{\uparrow}$ |                                                                |

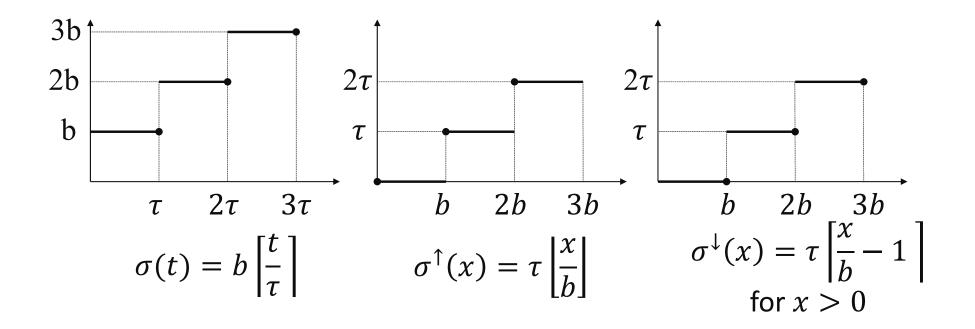

### Upper and Lower Pseudo-Inverses

$$f^{\uparrow}(x) = \sup \{t, f(t) \le x\} \qquad f^{\downarrow}(x) = \inf \{t, f(t) \ge x\}$$

$$f^{\downarrow}(x) = \inf \{t, f(t) \ge x\}$$

### Recap

arrival curve can be expressed with max-plus traffic envelope

g-regulation (e.g. LRQ) uses max-plus but cannot be expressed as arrival curve

the problem is not min-plus versus max-plus, but viewpoint: observe flow at an arbitrary point in time (or bit) versus observe at packet arrival time

## Viewpoint Equivalence Theorem max-plus formulation

**Theorem**: For a flow (A, L) the three conditions are equivalent

1. Flow has arrival curve constraint  $\sigma$

$$2. L_m + \dots + L_n \le \sigma^+(A_n - A_m)$$

3.

$$A_n - A_m \ge \sigma^{\downarrow}(L_m + \dots + L_n)$$

$$\sigma^{+}(t) = \lim_{s \to t, s > t} \sigma(s)$$

(right-limit)

## Viewpoint Equivalence Theorem max-plus formulation

For a flow (A, L) the three conditions are equivalent

1. Flow has max-plus traffic envelope  $\lambda$

$$2. L_m + \dots + L_n \leq \lambda^{\uparrow} (A_n - A_m)$$

3.

$$A_n - A_m \ge \lambda^-(L_m + \dots + L_n)$$

$$\lambda^{-}(x) = \lim_{y \to x, y < x} \lambda(y)$$

(left-limit)

Recall that  $\lambda = \sigma^{\uparrow}$ . Furthermore  $\lambda^{\uparrow} = \sigma^{+}$ ,  $\lambda^{-} = \sigma^{\downarrow}$

## Arrival Curve as Pi-regulation

Arrival curve constraint  $\sigma$  is equivalent to  $\Pi$ -regularity with

$$\Pi(A, L) = \max_{1 \le m \le n-1} \{A_m + \sigma^{\downarrow}(L_m + \dots + L_n)\}$$

e.g. Leaky bucket constraint

$$\Pi^{LB(r,b)}(A,L) = \max_{1 \le m \le n-1} \left\{ A_m + \frac{L_m + \dots + L_n - b}{r} \right\}$$

e.g. Staircase arrival curve

$$\Pi^{SC(\tau,b)}(A,L) = \max_{1 \le m \le n-1} \left\{ A_m + \tau \left[ \frac{L_m + \dots + L_n - b}{b} \right] \right\}$$

## **IEEE TSN Traffic Regulation Constraint**

At most K packets in an interval of  $\tau$  seconds.

This is  $\Pi$ -regularity with

$$\Pi^{TSN(\tau,K)}(A,L) = \max_{1 \le m \le n-1} \left\{ A_m + \tau \left[ \frac{n-m+1-K}{K} \right] \right\}$$

This is neither an arrival curve constraint nor g-regulation.

Other packet rate limits can be expressed as Pi-regulation (e.g. min spacing between packets, e.g. affine constraints)

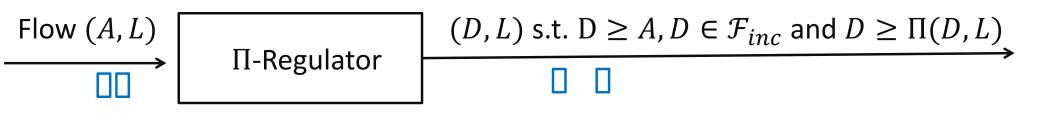

## Per-flow Minimal Pi-Regulator

$\Pi$ -Regulator is FIFO and transforms a flow into a  $\Pi$ -regular flow.

There is one Minimal  $\Pi$ -Regulator; it is defined by  $D_1=A_1$  and  $D_n=\max\{A_n,D_{n-1},\Pi(D)_n\}$

If regulation is "arrival curve constraint" the minimal  $\Pi$ -regulator is the packetized greedy shaper.

If regulation is "g-regulation" it is the minimal g-regulator.

## 3. Interleaved Regulator

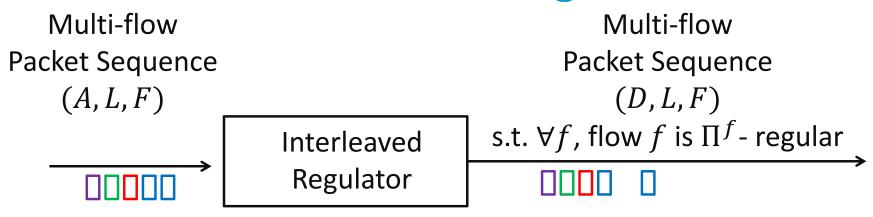

$A_n$ : arrival time of packet n;  $L_n$ : length;  $F_n$ : flow id of packet n An Interleaved regulator is a FIFO system such that every output flow f is  $\Pi^f$ - regular

$$D^f \ge \Pi^f (D^f, L^f)$$

where  $D^f$  is the subsequence of D obtained by keeping only dates that correspond to packets of flow f

## Minimal Interleaved Regulator

**Theorem**: There is one minimal interleaved regulator (i.e. such that  $D_n \leq D'_n$  for any other interleaved regulator).

It is given by  $D_1 = A_1$  and

$$D_n = \max \{A_n, D_{n-1}, \Pi^{F_n}(D^{F_n}, L^{F_n})_{I(n)}\}$$

where I(n) is the index of packet n in its flow.

# Implementation of Minimal Interleaved Regulator

$$D_n = \max\left\{A_n, D_{n-1}, \prod^{F_n} \left(D^{F_n}, L^{F_n}\right)_{I(n)}\right\} \text{ of packet at head of queue}$$

- One FIFO queue for all packets of all flows.

- Packet at head of queue is examined and delayed until it can be released while satisfying the regulation of its flow.

- Other packets wait until their turn comes.

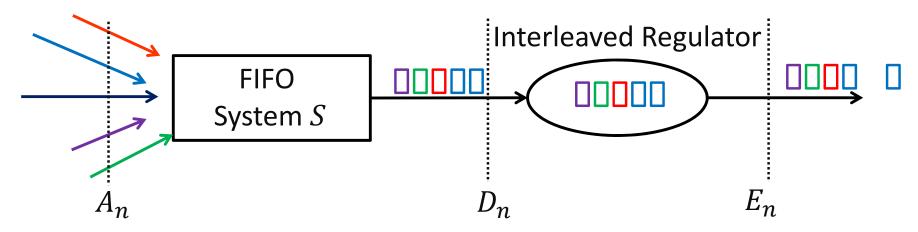

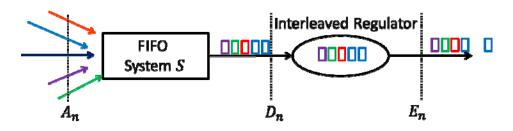

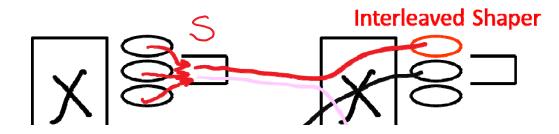

### Interleaved Regulator Does Not Increase Worst Case Delay

Every flow f is  $\Pi^f$  regular before input to S Output of S is fed to interleaved regulator with regulator  $\Pi^f$  for flow f

Theorem:

$$\sup_{n}(D_n - A_n) = \sup_{n}(E_n - A_n)$$

Interleaved Regulator is for free!

#### **Proof Outline**

Show by induction that  $E_n \leq A_n + d$  for any delay bound d on S. Fix n and let  $f = F_n$ , i = I(n) so that  $A_n = A_i^f$  and  $E_n = \max\left\{A_n, E_{n-1}, \Pi^f\left(E^f, L^f\right)_i\right\}$ . Show each term is  $\leq A_n + d$

- 1.  $A_n \leq A_n + d$  because  $d \geq 0$

- 2.  $E_{n-1} \le A_{n-1} + d$  (induction)  $\le A_n + d$

- 3.  $E_j^f \leq A_j^f + d$  for j < i (induction) thus ( $\Pi^f$  is causal, isotone, homog.)  $\Pi^f(E^f)_i \leq \Pi^f(A^f + d)_i = \Pi^f(A^f)_i + d$  (A, L) is  $\Pi^f$ -regular  $\Rightarrow \Pi^f(A^f)_i + d \leq A_i^f + d = A_n + d$

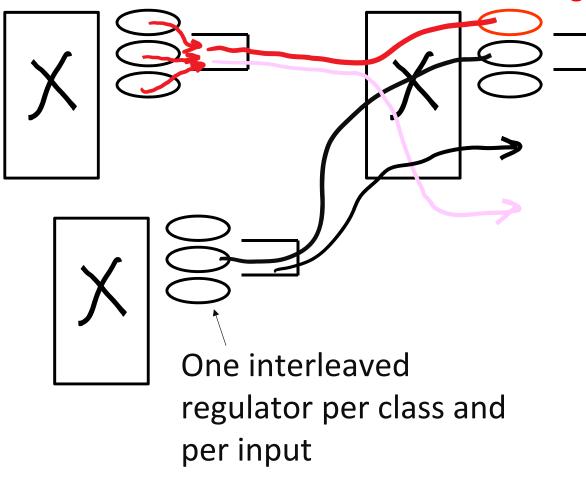

#### FIFO Network With Interleaved Regulators

#### **Interleaved Regulator**

[Specht-Samii 2016] places one interleaved regulator per input port before output queue.

Output of interleaved regulator has known burstiness

$\Rightarrow$  no burstiness cascade.

## Delay Computations in IEEE TSN

- Apply theorem where S = output scheduler at previous hop

- Worst case end-to-end queuing delay can ignore interleaved regulators. Delay bound at one interleaved regulator is absorbed by delay at previous hop.

- Queuing delay at every scheduler S (without shaper) can be computed easily since traffic is regular.

- Worst case delay at one node cannot ignore interleaved shaper.

⇒ Worst case end-to-end delay is generally less than sum of perhop delays.

#### Conclusions

Interleaved Regulators can be used to simplify and control FIFO networks.

Shaping-for-free is known for per-flow networks. Also holds for FIFO networks with interleaved regulators.

Pi-regulation generalizes arrival curves, g-regulation, packet rate limitations.

### References

[Bennett et al 2002] Bennett, J.C., Benson, K., Charny, A., Courtney, W.F. and Le Boudec, J.Y., 2002. Delay jitter bounds and packet scale rate guarantee for expedited forwarding. *IEEE/ACM Transactions on Networking (TON)*, 10(4), pp.529-540.

[Bondorf et al 2017], Bondorf, Steffen, Paul Nikolaus, and Jens B. Schmitt. "Quality and Cost of Deterministic Network Calculus: Design and Evaluation of an Accurate and Fast Analysis." *Proceedings of the ACM on Measurement and Analysis of Computing Systems* 1.1 (2017) and arXiv:1603.02094v3

[Bouillard-Stea 2015] Bouillard, A. and Stea, G., 2015. Exact worst-case delay in FIFO-multiplexing feed-forward networks. *IEEE/ACM Transactions on Networking (TON)*, 23(5), pp.1387-1400.

[Boyer et al 2012] Boyer, Marc, Nicolas Navet, and Marc Fumey. "Experimental assessment of timing verification techniques for AFDX." 6th European Congress on Embedded Real Time Software and Systems. 2012.

[Chang-Lin] Chang, C.S. and Lin, Y.H., 1998, May. A general framework for deterministic service guarantees in telecommunication networks with variable length packets. In *Quality of Service*, 1998.(IWQoS 98) 1998 Sixth International Workshop on (pp. 49-58). IEEE.

[Chang 2002] Chang, C.S., 2012. *Performance guarantees in communication networks*. Springer Science & Business Media

[Le Boudec 2018] Le Boudec, Jean-Yves, "A Theory of Traffic Regulators for Deterministic Networks with Application to Interleaved Regulators", arXiv preprint arXiv:1801.08477.

[Le Boudec-Thiran 2001] Le Boudec, Jean-Yves, and Patrick Thiran. *Network calculus: a theory of deterministic queuing systems for the internet*. Vol. 2050. Springer Science & Business Media, 2001, online at <a href="http://ica1www.epfl.ch/PS">http://ica1www.epfl.ch/PS</a> files/NetCal.htm

[Liebeherr 2017] Liebeherr, J., 2017. Duality of the Max-Plus and Min-Plus Network Calculus. *Foundations and Trends® in Networking*, 11(3-4), pp.139-282.

[Specht-Samii 2016] Specht, J. and Samii, S., 2016, July. Urgency-based scheduler for time-sensitive switched ethernet networks. In *Real-Time Systems (ECRTS), 2016 28th Euromicro Conference on* (pp. 75-85). IEEE.